闪存

| “flash memory”的各地常用名称 | |

|---|---|

| 中国大陆 | 闪存[1][2]、快闪存储器[3]、闪速存储器[4] |

| 台湾 | 快闪记忆体[5] |

| 计算机存储器类型 |

|---|

| 易失性存储器 |

| RAM |

| 发展中 |

| 历史上 |

| 非易失性存储器 |

| ROM |

| 非易失性随机存取存储器 |

| 早期非易失性随机存取存储器 |

| 磁式 |

| 光学式 |

| 发展中 |

| 历史上 |

闪存(英语:flash memory)是一种像电可擦写只读存储器一样的存储器,允许对资料进行多次的删除、加入或改写。这种内存广泛用于储存卡、U盘之中,因其可迅速改写的特性非常适合手机、笔记本电脑、游戏主机、掌机之间的文件转移,也曾经是数字相机、数字随身听和PDA的主要资料转移方式。

早期的闪存只要进行一次删除就会连带清除掉所有的资料,但目前已可以精确到对指定的资料进行单个删除。与传统的硬盘相比,闪存有更佳的动态抗震性,不会因为剧烈晃动而造成资料丢失;闪存在被做成储存卡时非常坚固牢靠,可以浸在水中,也可抵抗高压力和极端温度;并且闪存属于“非易失性固态存储”,非易失性指的是在保存文件时不需要消耗电力。基于以上这些优点,使得闪存非常适用于需要游历各种场所并需要随时存档的电子设备,因此在小型的可移动电子设备中大放异彩。闪存的出现迅速取代了造价高昂的普通EEPROM或需要保持供电才能保存数据的SRAM。

闪存在分类上属于“EEPROM”的一种,但一般业界所讲的EEPROM指的是那种“非快闪式”的普通EEPROM,并不是指它。闪存以“宏块抹除”的方式改写其体内的资料,因为这种宏块的特性导致它的“写入速度”往往慢于“读取速度”,但也导致它的成本远远低于“以字节为单位写入”的普通EEPROM[6]。由于普通EEPROM需要一个一个比特的删除已有资料,这让其传输速度极其缓慢,相较之下快闪记体直接使用“宏块抹除”则会快得多,在会多次用到高清画面、高质量音乐的情况下尤为明显。

闪存又分为NOR与NAND两型,闪存最常见的封装方式是TSOP48和BGA,在逻辑接口上的标准则由于厂商阵营而区分为两种:ONFI (页面存档备份,存于互联网档案馆)和Toggle。手机上的闪存常常以eMMC、UFS和NVME(特用于苹果设备中的闪存)的方式存在。

历史

[编辑]闪存(无论是NOR型或NAND型)是舛冈富士雄博士1980年申请了一个叫做simultaneously erasable EEPROM的专利。然而,东芝公司的论资排辈却让这项划时代的发明石沉大海,直到4年之后。“我终于被提拔了,可以不要批准就去工厂,让工人们帮忙做出样品了”,富士雄说。 据东芝表示闪存之所以命名为“Flash”是由舛冈博士的同事有泉正二建议,因为这种内存的抹除流程让他想起了相机的闪光灯。舛冈博士在1984年的加州旧金山IEEE国际电子器件会议(International Electron Devices Meeting, IEDM)上发表了这项发明。Intel看到了这项发明的巨大潜力,并于1988年推出第一款商业性的NOR Flash芯片。

NOR Flash需要很长的时间进行抹写,但是它提供完整的寻址与资料总线,并允许随机存取存储器上的任何区域,这使的它非常适合取代老式的ROM芯片。当时ROM芯片主要用来存储几乎不需更新的代码,例如电脑的BIOS或机顶盒(Set-top Box)的固件。NOR Flash可以承受一万到一百万次抹写循环,它同时也是早期的可移除式快闪存储媒体的基础。CompactFlash本来便是以NOR Flash为基础的,虽然它之后跳槽到成本较低的NAND Flash。

舛冈富士雄没有停止追求,在1986年发明了NAND Flash,大大降低了制造成本。由于他的贡献,东芝奖励了他一笔几百美金的奖金和一个位置很高却悠闲的职位。做为一个工程师,他忍受不了这种待遇,不得不辞职进入大学继续科研。东芝在1989年的国际固态电路会议(ISSCC)上发表了NAND Flash。NAND Flash具有较快的抹写时间,而且每个存储单元的面积也较小,这让NAND Flash相较于NOR Flash具有较高的存储密度与较低的每比特成本。同时它的可抹除次数也高出NOR Flash十倍。然而NAND Flash的I/O接口并没有随机存取外部地址总线,它必须以区块性的方式进行读取,NAND Flash典型的区块大小是数百至数千比特。

因为多数微处理器与微控制器要求字节等级的随机存取,所以NAND Flash不适合取代那些用以装载程序的ROM。从这样的角度看来,NAND Flash比较像光盘、硬盘这类的次级存储设备。NAND Flash非常适合用于储存卡之类的大量存储设备。第一款建立在NAND Flash基础上的可移除式存储媒体是SmartMedia,此后许多存储媒体也跟着采用NAND Flash,包括MultiMediaCard、Secure Digital、Memory Stick与xD卡。

在很长一段时间,东芝公司甚至不承认NOR flash是舛冈富士雄发明的,宣称是Intel发明的。直到IEEE在1997年颁给舛冈富士雄特殊贡献奖后才改口。舛冈富士雄觉得自己的贡献被东芝公司抹杀了,于2006年起诉了东芝公司,并索要10亿日元的补偿,最后和东芝公司达成和解,得到8700万日元(合758,000美元)。

运作原理

[编辑]

闪存将资料存储在由浮栅金属氧化物半导体场效应晶体管组成的记忆单元数组内,在单层存储单元(Single-level cell, SLC)设备中,每个单元只存储1比特的信息。而多层存储单元(Multi-level cell, MLC)设备则利用多种电荷值的控制让每个单元可以存储1比特以上的资料,这样提升了容量,降低价格,但是减少了寿命,性能下降,存储稳定性下降。目前已经量产TLC(Trinary-Level Cell)还有QLC产品,目前TLC还是主要使用的技术。

NOR Flash

[编辑]

闪存的每个存储单元与标准MOSFET类似,不同的是闪存的晶体管有两个而并非一个栅极。在顶部的是控制栅(Control Gate, CG),如同其他MOS晶体管。但是它下方则是一个以氧化物层与周遭绝缘的浮栅(Floating Gate, FG)。这个FG放在CG与MOSFET沟道之间。由于这个FG在电气上是受绝缘层独立的,所以进入的电子会被困在里面。在一般的条件下电荷经过多年都不会逸散。当FG抓到电荷时,它部分屏蔽掉来自CG的电场,并改变这个单元的阈值电压(VT)。在读出期间。利用向CG的电压,MOSFET沟道会变的导电或保持绝缘。这视乎该单元的VT而定(而该单元的VT受到FG上的电荷控制)。这股电流流过MOSFET沟道,并以二进制码的方式读出、再现存储的资料。在每单元存储1比特以上的资料的MLC设备中,为了能够更精确的测定FG中的电荷位准,则是以感应电流的量(而非单纯的有或无)达成的。

逻辑上,单层NOR Flash单元在默认状态代表二进制码中的“1”值,因为在以特定的电压值控制栅极时,电流会流经沟道。经由以下流程,NOR Flash单元可以被设置为二进制码中的“0”值:

- 1.对CG施加高电压(通常大于5V)。

- 2.现在沟道打开,所以电子可以从源极流入漏极(想像它是NMOS晶体管)。

- 3.源-漏电流够高了,足以导致某些高能电子越过绝缘层,并进入绝缘层上的FG,这种过程称为热电子注入。

由于漏极与CG间有一个大的、相反的极性电压,借由量子穿隧效应可以将电子拉出FG,所以能够地用这个特性抹除NOR Flash单元(将其重置为“1”状态)。现代的NOR Flash芯片被分为若干抹除片段(常称为区扇(Blocks or sectors)),抹除操作只能以这些区块为基础进行;所有区块内的记忆单元都会被一起抹除。不过一般而言,写入NOR Flash单元的动作却可以单一字节的方式进行。

虽然抹写都需要高电压才能进行,不过实际上现今所有闪存芯片是借由芯片内的电荷泵产生足够的电压,所以只需要一个单一的电压供应即可。

NOR Flash可以制作成立体结构,但尚未量产。

NAND Flash

[编辑]

与非门闪存(NAND闸缓冲存储器)利用穿隧注入写入,以及穿隧释放(Tunnel release)抹除。NAND Flash在U盘、储存卡与固态盘上都可看到。

3D NAND Flash

[编辑]将NAND闪存在垂直方向进行堆叠和互联,藉以提高单位面积的内存容量。[7]3D NAND会提高产品容量还有稳定性。

存储单元电位阶数划分

[编辑]通过对闪存内最小的物理存储单元的电位划分不同的阶数,可以在一个存储单元内存储一至多个二进制位数。常见的一至四层存储单元为SLC、MLC、TLC和QLC。

SLC

[编辑]传统上,每个存储单元内存储1个信息比特,称为单层存储单元(Single-Level Cell,SLC),使用这种存储单元的闪存也称为单层存储单元闪存(SLC flash memory),或简称SLC闪存。SLC闪存的优点是传输速度更快,功率消耗更低和存储单元的寿命更长。然而,由于每个存储单元包含的信息较少,其每兆字节需花费较高的成本来生产,大多数用在企业上,很少有消费型SLC存储设备拿来贩卖,富士通生产的FSX系列是首款使用SLC芯片消费型固态盘,在2014贩售。

MLC

[编辑]多层存储单元(Multi-Level Cell,MLC)可以在每个存储单元内存储2个以上的信息比特,其“多级”指的是电荷充电有多个能级(即多个电压值),如此便能存储多个比特的值于每个存储单元中。借由每个存储单元可存储更多的比特,MLC闪存可降低生产成本,但比起SLC闪存,其传输速度较慢,功率消耗较高和存储单元的寿命较低,因此MLC闪存技术会用在标准型的储存卡,也用在最常见的消费型固态盘和U盘上。另外,如飞索半导体的MirrorBit®技术,也是属于这一类技术。

TLC

[编辑]三层储存单元(Triple-Level Cell, TLC),这种架构的原理与MLC类似,但可以在每个储存单元内储存3个信息比特。TLC的写入速度比SLC和MLC慢,寿命也比SLC和MLC短(使用LDPC的话,约有1500次),大约1000次。[8]在使用3D技术取代微缩后,TLC(3D-TLC)成为市场主流。

QLC

[编辑]四层储存单元(Quad-Level Cell, QLC),每个存储单元有4个bits的格式,寿命为四者之中最短,大约只有500次。

在假设低电位表示二进制的0,高电位表示二进制的1时,SLC、MLC、TLC和QLC的电位及二进制值对比表。

在表中可以清楚的看到SLC、MLC、TLC和QLC技术分别将单个存储单元划分为2/4/8/16阶,拿来存储1/2/3/4个二进制位数。

| SLC闪存 | MLC闪存 | TLC闪存 | QLC闪存 | |||||||

| 电位情况 | 二进制值 | 电位情况 | 二进制值 | 电位情况 | 二进制值 | 电位情况 | 二进制值 | |||

| 低电位 | 0 | 最低电位 | 00 | 最低电位 | 000 | 最低电位 | 0000 | |||

| 次低电位 | 0001 | |||||||||

| 次低电位 | 001 | 第三低电位 | 0010 | |||||||

| 第四低电位 | 0011 | |||||||||

| 次低电位 | 01 | 第三低电位 | 010 | 第五低电位 | 0100 | |||||

| 第六低电位 | 0101 | |||||||||

| 第四低电位 | 011 | 第七低电位 | 0110 | |||||||

| 第八低电位 | 0111 | |||||||||

| 高电位 | 1 | 次高电位 | 10 | 第五低电位 | 100 | 第九低电位 | 1000 | |||

| 第十低电位 | 1001 | |||||||||

| 第六低电位 | 101 | 第十一低电位 | 1010 | |||||||

| 第十二低电位 | 1011 | |||||||||

| 最高电位 | 11 | 次高电位 | 110 | 第十三低电位 | 1100 | |||||

| 第十四低电位 | 1101 | |||||||||

| 最高电位 | 111 | 次高电位 | 1110 | |||||||

| 最高电位 | 1111 | |||||||||

| 表内数据为假设低电位表示二进制的0,高电位表示二进制的1时的情况。 | ||||||||||

不足之处

[编辑]区块抹除

[编辑]闪存的一种限制在于即使它可以单一字节的方式读或写入,但是抹除一定是一整个区块。一般来说都是设置某一区中的所有比特为“1”,刚开始区块内的所有部分都可以写入,然而当有任何一个比特被设为“0”时,就只能借由清除整个区块来恢复“1”的状态。换句话说闪存(特别是NOR Flash)能提供随机读取与写入操作,却无法提供任意的随机改写。不过其上的区块可以写入与既存的“0”值一样长的消息(新值的0比特是旧值的0比特的超集)。例如:有一小区块的值已抹除为1111,然后写入1110的消息。接下来这个区块还可以依序写入1010、0010,最后则是0000。可是实际上少有算法可以从这种连续写入兼容性得到好处,一般来说还是整块抹除再重写。尽管闪存的数据结构不能完全以一般的方式做更新,但这允许它以“标记为不可用”的方式删除消息。这种技巧在每单元存储大于1比特资料的MLC设备中必须稍微做点修改。

记忆耗损

[编辑]另一项闪存的限制是它有抹写循环的次数限制(大多商业性SLC闪存保证“0”区有十万次的抹写能力,但因为制造精度问题其他区块不保证,有可能还会出现完全无法使用的出厂坏块)。这个结果部分地被某些固件或文件系统为了在相异区块间分散写入操作而进行的计算写入次数与动态重對映所抵销;这种技巧称为耗损平衡(wear leveling)。另一种处理方法称为坏区管理(Bad Block Management, BBM)。这种方法是在写入时做验证并进行动态重测,如果有验证失败的区块就加以剔除。对多数移动设备而言,这些磨损管理技术可以延长其内部闪存的寿命(甚至超出这些设备的使用年限)。此外,丢失部分资料在这些设备上或许是可接受的。至于会进行大量资料读写循环的高可靠性资料存储应用则不建议使用闪存。不过这种限制不适用于路由器与瘦客户端(Thin clients)等只读式应用,这些设备往往在使用年限内也只会写入一次或少数几次而已。

读取干扰

[编辑]所使用的闪存读取方式随着时间的推移会导致在同一区块中相近的记忆单元内容改变(变成写入动作)。这即是所谓的读取干扰。会导致读取干扰现象的读取次数门槛介于区块被抹除间,通常为100,000次。假如连续从一个记忆单元读取,此记忆单元将不会受损,而受损却是接下来被读取的周围记忆单元。为避免读取干扰问题,闪存控制器通常会计算从上次抹除动作后的区块读取动作总次数。当计数值超过所设置的目标值门槛时,受影响的区块会被复制到一个新的区块,然后将原区块抹除后释放到区块回收区中。原区块在抹除动作后就会像新的一样。若是闪存控制器没有即时介入时,读取干扰错误就会发生,如果错误太多而无法被ECC机制修复时就会伴随着可能的资料丢失。[9][10]

写入(编程)干扰

[编辑]写入干扰(编程干扰)是指当对页(page)进行写入时,由于阈值电压接近的关系,相邻的位(bit)也被升高,从而造成相邻的位出错。闪存电荷非常不稳定,相邻存储电荷的悬浮门间会相互干扰,造成相邻悬浮门间的bit错误,MLC由于存在4组接近的电压,与SLC相比更容易受到干扰。现在的主控固件已经支持使用异或的方式尽可能的将数据打乱到尽量每个bit之间是互相反转的方式来尽可能减少这种情况对数据存储稳定性的干扰

低端访问

[编辑]闪存芯片的低端接口通常与透过支持外界的寻址总线行随机存取的DRAM、ROM、EEPROM等内存不同。NOR Flash本身为读取操作(支持随机存取)提供外部寻址总线;至于解锁、抹除与写入则须以区块-区块(Block-by-block)的方式进行,典型的区块大小为64、128或256字节。NAND Flash所有的动作都必须以区块性基础(Block-wise fashion)执行,包含读、写、解锁与抹除。

NOR Flash

[编辑]从NOR Flash读取资料的方式与从RAM读取资料相近,只要提供资料的地址,资料总线就可以正确的导出资料。基于以上原因,多数微处理器可以将NOR Flash当作原地执行(Execute in place, XIP)内存使用,这意味着存储在NOR Flash上的程序不需复制到RAM就可以直接执行。

由于NOR Flash没有原生坏区管理,所以一旦存储区块发生毁损,软件或驱动程序必须接手这个问题,否则可能会导致设备发生异常。在解锁、抹除或写入NOR Flash区块时,特殊的指令会先写入已绘测的记忆区的第一页(Page)。接着快闪存储芯片会提供可用的指令清单给实体驱动程序,而这些指令是由通用闪存接口(Common Flash memory Interface, CFI)所界定的。与用于随机存取的ROM不同,NOR Flash也可以用在存储设备上;不过与NAND Flash相比,NOR Flash的写入速度一般来说会慢很多。NOR Flash最常见用途之一就是BIOS ROM芯片。

NAND Flash

[编辑]东芝在1989年发表了NAND Flash架构,[11]这种内存的访问方式类似硬盘、储存卡之类的区块性存储设备,每个区块由数个页所构成。一般来说这些页的大小为512[12]或2048或4096字节。在各个页之间彼此的连接区域会有几个字节(一般而言是资料大小的1/32),这些空间用于存储错误修正码的校验和。以下是一些典型的区块大小:

- 每32个512+ 16位组的页为1个大小是16KB的区块

- 每64个2048+ 64位组的页为1个大小是128KB的区块[13]

- 每64个4096+128位组的页为1个大小是256KB的区块[14]

- 每128个4096+128位组的页为1个大小是512KB的区块

读取与写入动作可以以“页”为单位偏移量进行,抹除动作只能以“区块”为单位偏移量进行。NAND Flash还有一项限制就是区块内的资料只能序列性的写入。[来源请求] 操作次数(Number of Operations, NOPs)则代表“页”可以被写入的次数。目前MLC的NOPs是1;而SLC则是4。[来源请求] NAND Flash也需要由设备驱动程序软件或分离的控制器芯片来进行坏区管理,例如SD卡内部便包含实行坏区管理与耗损平衡的电路。当一个逻辑区被高阶软件访问时,逻辑区对应到实体区的工作则由驱动程序或控制器进行。

标准化

[编辑]开放式NAND型闪存接口工作小组(Open NAND Flash Interface Working Group (ONFI))已为闪存芯片开发完成一份标准化低端访问接口规格书。这份规格允许并确认了来自不同供应商的闪存器件间的互通性。《开放式闪存接口规格书版本1.0》[15]于2006年12月28日发布。规定着:

- 下列闪存集成电路封装型式的标准实体接口(接脚排列):TSOP-48、WSOP-48、LGA-52与BGA-63。

- 一组读取、写入、与抹除闪存芯片的标准命令集

- 一种自我识别的机制(相较于SDRAM内存模块的序列式存在侦测特性)

支持ONFI小组的主要闪存制造商包含有:海力士、英特尔、美光科技与恒忆,也有与闪存芯片结合器件的主要制造商。[16]

一群供应商,包含英特尔、戴尔与微软成立非易失性内存主控制器接口(Non-Volatile Memory Host Controller Interface (NVMHCI))工作小组。[17]此小组的目的是提供标准的非易失性内存软硬件程序设计接口,包含有连接到PCI Express总线的"快闪缓存"(flash cache)器件。

NOR型与NAND型闪存的差异

[编辑]

NOR型与NAND型闪存最主要的两个差异点如下:

- 连接个别记忆单元的方法不同

- 读取写入内存的接口不同(NOR型闪存允许随机存取,而NAND型闪存只能允许页访问)

以上两点是相关的NAND型闪存研发所做出的设计抉择。NAND型闪存发展的一个目标是为了减少所需的芯片面积来实现给定的闪存容量,从而降低每比特的成本,并推升芯片最大容量,如此就可与磁性存储设备相互竞争,如硬盘。

NOR和NAND型闪存由记忆单元间的内部连接结构而得名。[18]NOR型闪存内部记忆单元以平行方式连接到比特线,允许个别读取与程序化记忆单元。这种记忆单元的平行连接类似于CMOS NOR闸中的晶体管平行连接。NAND型闪存内部记忆单元以顺序方式连接,类似于NAND闸。顺序连接方式所占空间较平行连接方式为小,降低了NAND型闪存的成本。

NOR型闪存面世后,成为比现有的EPROM与EEPROM内存更经济、更方便的复写型只读存储器。因此,随机存取的读取电路是需要的。然而,NOR型闪存当成只读存储器使用时的读取次数在预期上通常远大于写入次数,所以其内含的写入电路是相当慢的,并且只提供区块抹除功能。另一方面,使用闪存的应用,如取代硬盘,无需字符组层级的地址线,因为字符组层级的地址线只会增加无谓的复杂度与成本。

因为采用顺序连接方式及去除字符组的接触点,NAND型闪存记忆单元的大型闸格所占面积只有NOR型记忆单元的60%[19](假设采用相同的CMOS工艺,如130nm、90nm或65nm)。NAND型内存的设计者理解到闪存的面积,在移除外部地址线及资料总线电路后,将可进一步缩小。取而代之的是,外部设备可使用顺序访问命令与资料寄存器与NAND型闪存沟通,由内存内部获取所需资料并将其输出。选择这种设计方式使得NAND型闪存无法随机存取,但是NAND型闪存的主要目标是取代硬盘,而不是只读存储器。

写入续航力

[编辑]

NOR型闪存SLC浮闸的写入续航力通常大于或等于NAND型闪存,然而MLC NOR型与NAND型闪存有着相近的续航能力。

NAND型与NOR型闪存规格书所提供的写入续航周期速率如下:

- SLC NAND型闪存的续航率通常落在10万次(Samsung OneNAND KFW4G16Q2M)

- MLC NAND型闪存对于早期中型容量应用的续航力通常落在5千至1万次(Samsung K9G8G08U0M),对于后期大型容量应用的续航率则落在1千至3千次。

- TLC NAND型闪存的续航率通常落在1千次或更多(Samsung 840);以多层结构取代微缩及采用LDPC校正、都延长了续航率。

- QLC NAND型闪存的续航率可以达到5百至1千次。

- SLC浮栅NOR型闪存通常有着10万至百万次的写入续航率(Numonyx M58BW 100k; Spansion S29CD016J 1,000k)

- MLC浮栅NOR型闪存通常有着10万的写入续航率(Numonyx J3 flash)

以上数据只是大概的标称数值,实际写入寿命与不同厂商的产品技术及定位有关。使用更细微化的制程,可以提高产品读写性能和容量,但同时在写入寿命方面可能会面临更大的挑战。使用如记忆损耗调节及写入放大的特定算法及设计示例,可以用来调节存储系统的续航率来符合特定的需求。[20]损耗平衡是闪存产品使用寿命的必要保证,在U盘和固态盘等产品中,均有相关支持。

闪存文件系统

[编辑]因为闪存的独特特性,最好使用一个额外的控制器来实行记忆耗损平衡与错误修正(目前绝大多数SSD的主控自带闪存寿命磨损均衡功能和管理ECC纠错区域)或是一个特别设计的闪存文件系统,来将对媒体的写入动作与NOR闪存区块的长抹除时间的处理动作分开。闪存文件系统的背景观念如下:当闪存的存储内容被更新时,主控将欲改变的资料写入一个新的区块,创建地址对应,然后找时间抹除旧有的标记删除的区块(现在支持TRIM指令的SSD可以使用TRIM指令整理已经标记删除的块)。

特别的是,闪存文件系统只使用于MTDs(memory technology devices),此设备具有内嵌式闪存,但没有控制器。便携式快闪储存卡与U盘均有内置控制器来实行记忆耗损平衡与错误修正,所以使用特别的闪存文件系统并不会增加任何的好处。

多数情况下,闪存与计算机间存在一个中间层(大多数为主控芯片),将闪存模拟成磁盘使用。对于上层软件和用户来说,并不需要关心闪存的实际细节。

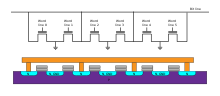

容量

[编辑]一般采用多颗闪存芯片组成数组的方式来达到增高容量的目的[21],这种方式使用于消费性电子产品中,如多媒体拨放器或全球定位系统中。因为闪存属于集成电路,所以闪存芯片的容量通常遵循摩尔定律。闪存可以通过工艺的进化和3D IC多层堆叠的方式获得更高的容量。但是闪存工艺到16nm以下时会出现严重漏电,导致内部短路或者写入时干扰其它块,所以目前的闪存工艺大部分是16nm到24nm之间以防止过高的漏电。而在市售的闪存封装产品中,可以通过包含多个闪存晶体(称为多管芯)来获得更高的容量。控制器可以通过不同的CE信号,选择不同的管芯进行操作。

消费性闪存存储设备一般使用2的整数次幂(2、4、8等等)来标示可使用的容量大小,而最终以兆字节(MB)或十亿字节(GB)来表示,例如:512MB,8GB。然而如欲取代传统硬盘(HDD)的固态盘(SSD)设备则是使用10的整数倍数来表示容量大小,如1,000,000字节与1,000,000,000字节,这是因为传统硬盘标示容量大小即是使用10进制词头。因此,固态盘上标示"64GB",则表示实际上至少有64×1,0003字节(64GB),通常更大一些。大部分用户则会感到容量稍少于他们的文件,这是因为主控的固件信息和坏块使用了一些空间。同时,一些操作系统容量标记的标记与生产商的标记方式不同也造成了此问题(混淆MB和MiB)。

闪存芯片内部的容量大小是以2进位倍数计算,但并非所有实际容量空间均能被驱动器接口所使用。闪存芯片实际的容量会大于出厂可用容量,或者说,可用容量会小于芯片容量,这是为了存放写入的闪存寿命磨损均衡表(FTL)(记忆损耗平衡)、出厂预留空间、分区表、错误修正码、及设备内部固件程序运算所需要的其他中继资料。

2005年,东芝与闪迪公司使用多层存储单元(multi-level cell,MLC)技术开发出可存储1GB资料量的NAND型闪存芯片,MLC拥有在最小记忆单元中存储两个比特资料的能力。2005年9月,三星电子宣布开发出世界上第一颗2GB闪存芯片。[22]

2006年3月,三星电子宣布开发出容量为4GB的固态盘机,比笔记本电脑所使用的同样容量硬盘还要来的小。2006年9月,三星电子宣布使用40纳米工艺量产8GB闪存芯片。[23]

2008年1月,闪迪公司宣布16GB的MicroSDHC与32GB的SDHC Plus储存卡开始贩售。[24][25]

2012年后的闪存存储设备有了较大的容量,如64、128及256GB。[26][27]一些更大容量的固态盘,根据容量大小,能被使用来当作整个电脑的备份硬盘。

仍有小容量的闪存芯片生产以供BIOS-ROM与嵌入式应用使用,容量大小约为1MB或以下。

传输速率

[编辑]

NAND型闪存卡的读取速度远大于写入速度。

当芯片磨损,抹除与程序的操作速度会降到相当慢,主控需要需要更大电压进行操作和更长的时间保证数据完整和创建ECC数据。传递多个小型文件时,若是每个文件长度均小于闪存芯片所定义的区块大小时,因为每次擦写一整个块,导致写入时需要将已有数据移至空闲的区域,每次读写都需要操作多次,就可能导致很低的传输速率。访问的迟滞也会影响性能,但还是比硬盘的迟滞影响小。但是在现有的分区的文件系统中,已经开始默认以闪存和Advanced format扇区配机械硬盘相同的4096字节为一个扇区对齐闪存块和机械硬盘的物理扇区进行扇区读写解决这个问题,每次当写入数据小于一个扇区时,会将不足一个扇区的数据写入后的扇区空闲空间置空,并且下次写入一个文件的时候只能单独再使用一个扇区以防止二次读写同一个块挪动数据导致的写入缓慢。

有些时候速度以MB/s(每秒兆字节)表示,或是以旧式单速光盘驱动器速度的倍数表示,如60×、100×或150×。在这里,1×等于150KB/s。举例来说,100×的储存卡的传输速率为150kB/s×100 = 15,000kB/s。

闪存控制器的质量也是影响性能的因素之一。即使闪存只有在制造时做缩小晶粒(die-shrink)的改变,但如果欠缺合适的控制器,就可能引起速度的降级。[28]

不同种类、不同工艺、不同技术水平的NAND闪存在读写速率上存在差异,同时,闪存产品的读写性能也与读写方式有关。一般闪存的数据接口为8位或者16位,其中8位较为常见。如果产品支持多沟道并行读写,那么就会有更高的速度。同时,若产品支持DDR、interleave技术,也可以提高速度。DDR是存储产品在主频(clock)上升沿和下降沿都可以读写数据,从而提高性能。interleave是存储产品内不同bank或plane间交错读写,控制器在操作对象尚处于忙状态时,即可以转到另一方进行操作,从而提高速度。如果同类闪存中有异步模式和同步模式之分,其中同步模式的读写速度会更快。

应用

[编辑]序列接口闪存

[编辑]

序列接口闪存是一种使用序列式接口(通常使用序列周边接口总线(SPI))来循序访问资料内容,小型且低功率的闪存。当其使用于嵌入式系统上时,序列式闪存比平行式闪存在印刷电路板上所需的连接线数要少得多;因为序列式接口可以一次同时发送与接受资料的一个比特,这使得序列式闪存具有减少在印刷电路板上所占面积、耗电量及整体系统成本的优势。

有好几个理由说明了为何使用较少外部接脚的序列式器件,而不是使用平行式器件,可以大大的降低整体的成本:

- 许多特殊应用集成电路是受接垫所限制的〈Pad-limited〉,意思是晶粒的大小是由引线键合接垫的数量所决定,而不是由器件逻辑门数及功能复杂度所决定。减少键合接垫数自然允许更精简的集成电路在更小的晶粒上;这也增加了晶圆上所能制造出的晶粒数量,同时也降低了单位晶粒的成本。

- 减少了外在接脚的数目,同时降低了IC组装及封装的成本。序列式接口器件比平行式接口器件所使用的封装型式来的小且简单。

- 封装型式小及较低的外在接脚数目,所以占据的PCB面积也小。

- 较少的外在接脚数目,也简化了PCB上绕线的复杂度。

SPI闪存的型式主要有两种:一种是小页特性且内含一个或多个内部SRAM的页缓冲器,能够让整个页的资料都读入缓冲器、修改部分资料、而后再写回闪存中(例如Atmel的DataFlash:AT45,Micron Technology页抹除NOR型闪存)。另一种则有较大的区段。一般来说,SPI闪存的最小区段大小是4kB,最大可达64kB。因为此类SPI闪存缺乏内部SRAM缓冲器,修改资料时必须将完整的资料页读出,再修改资料后,写回闪存中,使得管理速度变慢。SPI闪存比平行式接口闪存便宜,因此应用于具有程序代码對映(Code-Shadowing)功能的系统上,是一个不错的选择。

而这两种型式的闪存不容易做到简单的直接置换,因为没有相同的外部接脚且命令集也互不兼容。

固件存储

[编辑]

随着现下CPU的速度越来越快,平行式接口闪存器件的速度通常远小于与其连接的电脑系统内存总线速度。相较之下,目前的SRAM访问的时间通常小于10ns,而DDR2 SDRAM访问时间一般则小于20ns。因为这个因素,一般合理的使用方式是将要存放于對映内存里的代码预先存放于闪存中,并在CPU执行代码前将闪存中的代码复制到對映内存中,如此一来,CPU就可以用最高速度来取用代码。设备上的固件也可以预先存放于序列式接口闪存中,在设备开机后,将其复制到SDRAM或SRAM里。[29]使用外部序列式闪存而不用芯片中内嵌闪存是因为芯片工艺上的考虑而妥协的结果(适用于高速逻辑工艺通常不适用于闪存,反之亦然)。如果有需要将一个宏块的固件代码读入时,通常会事先将代码压缩后再存入闪存中,就可以缩小闪存芯片上被使用的区域。典型的序列式接口闪存应用于固件存储上有:硬盘、以太网控制器、DSL调制解调器、无线网卡等等。对于UEFI而言,因为在UEFI启动过程的DXE阶段前UEFI对主存储器的访问有限,所以UEFI固件通常保存在NOR Flash中。

闪存作为硬盘的替代品

[编辑]

近期另一个闪存的应用就是作为硬盘的替代品。因为闪存没有硬盘驱动器械因素的限制并且可以多单元并行访问,所以固态盘(SSD)在速度、噪音、耗电量与可靠度等因素的考量上是非常吸引人的。闪存器件正获取便携式行动设备上第二存储器件的地位。同时使用在高性能台式机及一些具有RAID和SAN架构的服务器上作为硬盘的替代品。

但是以闪存为基础的固态盘,也存在其他方面因素,使得它并不具有吸引力。例如闪存每千兆比特的成本依旧比硬盘高出许多。[30]另一个不具吸引的因素就是闪存有着有限的P/E循环次数,但是这个因素可以透过程序优化,目前似乎已在人为控制能力范围内,加上容量的增大使得每单位读写次数减少,让它的使用寿命可以达到传统硬盘甚至更高的水准,因此以闪存为基础的固态盘也施行了与现有硬盘相同的保固政策。[31]

对于关系性数据库或其他使用ACID的数据库事务系统上,即使是使用目前最慢的闪存存储媒体也可以比使用硬盘所组成的数组,在速度的表现上有着显著的提升。[32][33]

于2006年6月,三星发布第一批配备闪存固态盘的个人电脑:Q1-SSD及Q30-SSD,均使用32GB的固态盘,并且初期只在韩国地区发售。[34]

在2008年,固态盘成为第一版MacBook Air的选用配备,并且从2010年起,固态盘成为所有Macbook Air笔记本电脑的标准配备。2011年后开始,由于固态盘成为Intel所倡议超极本的一部分,超薄笔记本电脑以固态盘为标准配备的数量逐渐增加。因为固态硬盘的性能远高于机械硬盘,所以2011年以后固态硬盘在PC上逐步得到普及。

也有混合型技术,诸如混合型硬盘和ReadyBoost,尝试将两种技术的优点合并,使用闪存作为硬盘上常用且鲜少修改的文件,如应用程序及操作系统的可执行文件,的高速非易失性缓存;或者使用固态硬盘加快机械硬盘的读写速度。

闪存作为随机存取存储器

[编辑]截至2012年,有许多的尝试想把闪存作为电脑的主存储器,动态随机存取存储器(DRAM)。[35]在这个应用角色上,闪存的速度是比现有的DRAM慢,但是耗电量却远小于DRAM。但是闪存的寿命也是需要注意的问题。闪存的寿命通常是几千次P/E,而RAM的寿命几乎是无尽的P/E次数,闪存寿命耗尽有可能会导致数据丢失,系统崩溃。

新型存储介质

[编辑]2015年,英特尔及美光联合发布了xPoint新型存储介质,这种介质是一种相变存储材料(而非NAND或者Nor),当下主要用于英特尔的Optane固态硬盘中。

工业产值

[编辑]2008年,一份资料中表示闪存在制造与销售上的工业产值约为US$91亿。2006年,另一些资料将闪存市场规模预估为超过US$200亿,这是根据整体半导体市场超过8%与全部半导体内存市场超过34%的成长。[36]

根据DRAMeXchange的研究报告,2007年全球Flash产业的市场规模为133亿6千8百万美元,2008年则是114亿1千8百万美元,整体营收降低了14.6%,主要的原因是受到产品平均单价下滑的影响。[37]

根据DRAMeXchange于2009年2月所发布的2008年全年NAND型闪存品牌厂商营收排名资料,第一为韩国厂商三星(Samsung)市占率高达40.4%(46亿1千4百万美元),其次是日本厂商东芝(Toshiba)的28.1%(32亿5百万美元),第三是韩国厂商Hynix的15.1%(17亿2千7百万美元),第4为美国厂商美光(Micron)7.9%(8亿9千7百万美元),第5为美国厂商英特尔(Intel)5.8%(6亿6千万美元),第6是欧洲厂商恒忆(Numonyx,STMicro)2.6%(营收为2亿9千5百万美元)。[38]

于2012年,预估闪存市场落在$268亿。[39]然而根据2013年4月DRAMeXchange的调查数据显示,2012年全年NAND型闪存品牌厂商总营收落在190亿6千2百万美元,较2011年衰退6.6%。[40]

现今技术发展

[编辑]

由于NAND型闪存本身相对简单的结构及对高容量的高需求关系,使它成为电子器件中,在技术规模上发展最积极的。只有少数几家顶尖的制造商能够在高度的竞争中,积极的开发出缩小设计规则或是工艺技术里程点。 [10]虽然原始版本摩尔定律所预测尺寸缩小一半时程因子为每三年,但是在近期NAND型闪存的例子上这个因子却是每两年。

于2012年11月,三星宣布已经开始量产10nm的芯片,这暗示著最小几何形状介于10至19nm间。[41][42]

由于闪存的最小组成器件已被最小化到极致的关系,未来的闪存密度的增加,将依靠更高级别的MLC,或是多层堆栈与工艺的改善来驱动。从缩小尺寸伴随而来的耐久性降低与不正确比特误码率增加,这些都可以借由改善错误修正机制来弥补。[43]即使有了这些进步,已有经济规模的闪存在尺寸上也难以越来越小。闪存本身的读写速度有限,并且有写入次数限制。有些具有光明展望的新技术(诸如铁电随机存取存储器(FeRAM)、磁阻式随机存取存储器(MRAM)、可编程金属化单元(PMC)、电阻式存储器(ReRAM)、相变化内存(PCM)与其他)均在探索与研发中,希望能更大规模的取代闪存。[44]

随着NAND制程越来越小,缩短制程提高存储密度已经非常困难。最新的NAND技术被称为3D-NAND,这种材料改变了2D-NAND单层的设计,将32层、64层NAND进行堆叠,从而提高存储密度。当前美光、SK-海力士、东芝、西部数据、三星几大NAND厂商均已拥有自己的3D-NAND产品。第一代基于3D-NAND的固态硬盘也已经开始广泛应用于数据中心和消费级计算机。借助3D-NAND,固态硬盘容量得到了质的提升,在2017年中国国内一家厂商Memblaze发布的PBlaze5 PCIe SSD已经最高可以做到11TB可用容量[45]。

参见

[编辑]参考文献

[编辑]- ^ 闪存. 术语在线. 全国科学技术名词审定委员会. (简体中文)

- ^ 教育部教育考试院.全国计算机等级考试二级教程:公共基础知识 [M].北京:高等教育出版社, 2022 (2023-05): 8.

- ^ 顾馨蕊,谢雨来.快闪存储器 (页面存档备份,存于互联网档案馆) [DB/OL].冯丹,陈云霁,陈文光,等编 (2022-01-20) [2024] // 陈奎元.中国大百科全书. 3版网络版.北京:中国大百科全书出版社.

- ^ 闪速存储器. 术语在线. 全国科学技术名词审定委员会. (简体中文)

- ^ flash memory. 乐词网. 国家教育研究院 (中文(台湾)).

- ^ 存档副本. [2017-10-26]. (原始内容存档于2021-05-07).

- ^ Samsung ships first 3D vertical NAND flash, defies memory scaling limits. [2013-08-14]. (原始内容存档于2019-11-28).

- ^ 三星大规模生产128Gb MLC闪存芯片. MyDrivers. [2013-10-17]. (原始内容存档于2013-10-17).

- ^ TN-29-17 NAND Flash Design and Use Considerations Introduction (PDF). Micron. April 2010 [29 July 2011]. (原始内容 (PDF)存档于2011-07-19).

- ^ 10.0 10.1 Kawamatus, Tatsuya. TECHNOLOGY FOR MANAGING NAND FLASH (PDF). Hagiwara sys-com co., LTD. [1 August 2011].[失效链接]

- ^ TOSHIBA ANNOUNCES 0.13 MICRON 1GB MONOLITHIC NAND. [2013-08-03]. (原始内容存档于2012-12-27) (英语).

Toshiba invented NAND flash technology in 1989

- ^ Kim, Jesung; Kim, John Min; Noh, Sam H.; Min, Sang Lyul; Cho, Yookun. A Space-Efficient Flash Translation Layer for CompactFlash Systems (PDF). Proceedings of the IEEE 48 (2). 2002-05: 366–375 [15 August 2008].

- ^ TN-29-07: Small-Block vs. Large-Block NAND flash Devices 互联网档案馆的存档,存档日期2013-06-08. Explains 512+16 and 2048+64-byte blocks

- ^ AN10860 LPC313x NAND flash data and bad block management (页面存档备份,存于互联网档案馆) Explains 4096+128-byte blocks.

- ^ Open NAND Flash Interface Specification (PDF). Open NAND Flash Interface. 28 December 2006 [31 July 2010]. (原始内容 (PDF)存档于2011-07-27).

- ^ A list of ONFi members is available at The ONFI Workgroup Membership (页面存档备份,存于互联网档案馆).

- ^ Dell, Intel And Microsoft Join Forces To Increase Adoption Of NAND-Based Flash Memory In PC Platforms. REDMOND, Wash: Microsoft. 2007-05-30 [2013-08-03]. (原始内容存档于2014-08-12) (英语).

- ^ See pages 5–7 of Toshiba's "NAND Applications Design Guide" under External links[锚点失效].

- ^ Pavan, Paolo; Bez, Roberto; Olivo, Piero; Zononi, Enrico. Flash Memory Cells – An Overview (PDF). Proceedings of the IEEE 85 (8). 1997: 1248–12711997-08 [15 August 2008]. doi:10.1109/5.622505.

- ^ NAND Evolution and its Effects on Solid State Drive Useable Life (PDF). Western Digital. 2009 [22 April 2012]. (原始内容 (PDF)存档于2011-11-12).

- ^ Flash vs DRAM follow-up: chip stacking. The Daily Circuit. 22 April 2012 [22 April 2012]. (原始内容存档于2012-11-24).

- ^ Shilov, Anton. Samsung Unveils 2GB Flash Memory Chip. X-bit labs. 12 September 2005 [30 November 2008]. (原始内容存档于2008-12-24).

- ^ Gruener, Wolfgang. Samsung announces 40 nm Flash, predicts 20 nm devices. TG Daily. 11 September 2006 [30 November 2008]. (原始内容存档于2008年3月23日).

- ^ 12 GB MicroSDHC. [2013-07-05]. (原始内容存档于2008-12-19).

- ^ 32 GB SDHC Plus. [2013-07-05]. (原始内容存档于2008-12-19).

- ^ Bruce Gain. Look Out for the 256GB Thumb Drive and the 128GB Tablet. PCWorld. 2011-04-16 [2013-08-03]. (原始内容存档于2012-01-21) (英语).

- ^ Matt Burns. Kingston outs the first 256GB flash drive. TechCrunch. 2009-07-20 [2013-08-13]. (原始内容存档于2021-04-15) (英语).

- ^ Samsung Confirms 32nm Flash Problems, Working on New SSD Controller 互联网档案馆的存档,存档日期2016-03-04.

- ^ Many serial flash devices implement a bulk read mode and incorporate an internal address counter, so that it is trivial to configure them to transfer their entire contents to RAM on power-up. When clocked at 50 MHz, for example, a serial flash could transfer a 64 Mbit firmware image in less than two seconds.

- ^ Lyth0s. SSD vs. HDD. elitepcbuilding.com. 17 March 2011 [11 July 2011]. (原始内容存档于2011-08-20).

- ^ Flash Solid State Disks – Inferior Technology or Closet Superstar?. STORAGEsearch. [30 November 2008]. (原始内容存档于2008-12-24).

- ^ "Intel SSD 910 vs HDD RAID in tpcc-mysql benchmark.". [2013-08-02]. (原始内容存档于2014-07-05).

- ^ Matsunobu, Yoshinori. "SSD Deployment Strategies for MySQL." (页面存档备份,存于互联网档案馆) Sun Microsystems, 15 April 2010.

- ^ Samsung Electronics Launches the World’s First PCs with NAND Flash-based Solid State Disk. Press Release. Samsung. 24 May 2006 [30 November 2008]. (原始内容存档于2008-12-20).

- ^ Douglas Perry (2012) (页面存档备份,存于互联网档案馆) Princeton: Replacing RAM with Flash Can Save Massive Power.

- ^ Yinug, Christopher Falan. The Rise of the Flash Memory Market: Its Impact on Firm Behavior and Global Semiconductor Trade Patterns (PDF). Journal of International Commerce and Economics. July 2007 [19 April 2008]. (原始内容 (PDF)存档于2008-05-29).

- ^ DRAMeXchange reports 4Q08 and 2008 Sales Ranking of NAND Flash Brand Companies. DRAMeXchange. 2009-02-06 [2013-08-03]. (原始内容存档于2009-07-22) (英语).

- ^ 集邦:NAND Flash品牌廠商公佈去年第四季暨全年營收排名. DRAMeXchange. 2009-02-05 [2013-08-03]. (原始内容存档于2009-07-30) (中文(台湾)).

- ^ NAND memory market rockets (页面存档备份,存于互联网档案馆), April 17, 2013, Nermin Hajdarbegovic, TG Daily, retrieved at 18 april 2013

- ^ 2012年第四季NAND Flash品牌供货商营收季成长14.6%,全年衰退6.6%. DRAMeXchange. 2013-04-02 [2013-08-03] (中文(中国大陆)).[永久失效链接]

- ^ Humphries, Matthew (15 November 2012)."Samsung starts producing 10nm NAND memory chips" (页面存档备份,存于互联网档案馆) Geek.com.Retrieved 18 November 2012.

- ^ Clarke, Peter (20 November 2012). "Samsung takes NAND memory below 20-nm" (页面存档备份,存于互联网档案馆) eetimes.com. Retrieved 21 December 2012.

- ^ Lal Shimpi, Anand. Micron's ClearNAND: 25nm + ECC, Combats Increasing Error Rates. Anandtech. 2 December 2010 [2 December 2010]. (原始内容存档于2010-12-03).

- ^ Kim, Kinam; Koh, Gwan-Hyeob. Future Memory Technology including Emerging New Memories (PDF). Serbia and Montenegro: Proceedings of the 24th International Conference on Microelectronics. 16 May 2004: 377–384 (2004-05) [15 August 2008].

- ^ 形态与性能双优 Memblaze PBlaze5 PCIe NVMe SSD聚焦闪存新革命-IT168 存储专区. storage.it168.com. [2018-03-13]. (原始内容存档于2020-12-14).

外部链接

[编辑]- 给Linux系统的快闪文件系统(英文)

- 介绍YAFFS,首个NAND闪存专用文件系统(英文)

- YAFFS - Yet Another Flash Filing System, is a filing system optimised for NAND Flash chips (GPL)(英文)

- Memory Technology Device (MTD) Subsystem for Linux (页面存档备份,存于互联网档案馆)(英文)

- 快闪存储器如何工作 (页面存档备份,存于互联网档案馆)(英文)

- HDD Repair Tool(英文)

- Linux内存技术设备──NAND (页面存档备份,存于互联网档案馆)(英文)

- STMicroelectronics官网 (页面存档备份,存于互联网档案馆)(英文)

- 开放式NAND型闪存接口 (页面存档备份,存于互联网档案馆)(英文)

- Cypress半导体(英文)

- How to Custom USB Flash Drive (英文)

- China USB Flash Drive (英文)