或非门

| 基本逻辑闸 | |

| 缓冲 | 非 |

| 与 | 与非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蕴含 | 蕴含非 |

| 输入 A B |

输出 A NOR B | |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

或非门(英语:NOR gate)是数字逻辑中实现逻辑或非的逻辑门,功能见右侧真值表。若输入均为低电平(0),则输出为高电平(1);若输入中至少有一个为高电平(1),则输出为低电平(0)。或非是逻辑或加逻辑非得到的结果。或非是一种具有函数完备性的运算,因此其他任何逻辑函数都能用或非门实现。相比之下,逻辑或运算器是一种单调的运算器,其只能将低电平变为高电平,但不能将高电平变为低电平。

在绝大多数但不是所有的电路设计中,逻辑非的功能本身就包含在结构中,如CMOS和TTL等。在这样的逻辑系列中,要实现或门,唯一的方法是用2个或更多的逻辑门来实现,如一个或非门加一个反相器,但一个重要的例外是多米诺逻辑,因为其结构中本身就没有反相逻辑。

概述

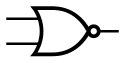

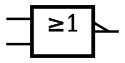

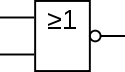

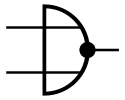

[编辑]下列包括逻辑门的3种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)和不再使用的DIN符号(DIN 40700)。其他的逻辑门符号见逻辑门符号表。

| 表达式 | 符号 | 功能表 | 继电器逻辑 | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | |||||||||||||||||||||||

|

|

|

|

| |||||||||||||||||||||

硬件描述和引脚分配

[编辑]或非门是基本的门电路,因此常用于晶体管-晶体管逻辑(TTL)和CMOS集成电路。标准4000系列CMOS集成电路是4001,包含四个2输入或非门。引脚分配如下:

|

|

可用型号

[编辑]大多数半导体制造商都生产这种器件,如飞兆半导体公司、飞利浦、德州仪器,封装方式分为直插DIP封装和SOIC封装两种。器件的数据表可在大多数器件数据库查询到。

常用的CMOS和TTL逻辑系列中,也有8输入或非门:

- CMOS

- 4001:四2输入或非门

- 4025:三3输入或非门

- 4002:双4输入或非门

- 4078:单8输入或非门

- TTL

- 7402:四2输入或非门

- 7427:三3输入或非门

- 7425:双4输入或非门(有闸门,已不再使用)

- 74260:双5输入或非门

- 744078:单8输入或非门

实现

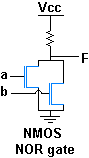

[编辑] |

|

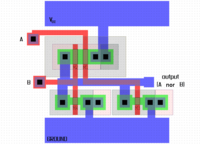

上图展示了使用NMOS线路的2输入或非门的构造。如果输入都是高电平,对应的NMOS就会接通,输出会被拉到低电平;反之输出会通过上拉电阻被拉到高电平。下图展示了使用CMOS技术的2输入或非门。输出端的二极管和电阻用来保护CMOS器件,以防其受到静电放电(ESD)的损害,从而在电路的逻辑功能中发挥不了作用。

备选方案

[编辑]

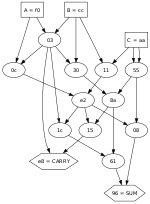

如果没有专门的或非门,可以用与非门实现或非门,方法是将两个输入接在一起的与非门作为另外一个与非门的两个输入,然后在后者的输出接一个输入接在一起的与非门,即可实现或非门。任何逻辑门都可以用与非门的组合或或非门的组合实现。

或非逻辑

[编辑]与非门实现的或非门逻辑函数如下:

或非门具有函数完备性,和与非门一样可以仅用其实现其他所有的逻辑功能。

| NOT(非) | |||

| AND(与) | |||

| NAND(与非) | |||

| OR(或) | |||

| NOR(或非) | |||

| XOR(异或) | |||

| XNOR(同或) | |||

| 蕴涵 | |||

| 等价 | |||

| 重言式 | |||

| 矛盾式 |

![{\displaystyle x{\overline {\lor }}y=\left[\left(x{\overline {\land }}x\right){\overline {\land }}\left(y{\overline {\land }}y\right)\right]{\overline {\land }}\left[\left(x{\overline {\land }}x\right){\overline {\land }}\left(y{\overline {\land }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/38fd5c77550c8a7d8c14d77bc5d4f8217dd70e64)

![{\displaystyle \left[\left(x{\overline {\lor }}x\right){\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/dba7191b0cae3237e54871465a794c731d51ae2a)

![{\displaystyle \left(x{\overline {\lor }}y\right){\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0f22f755c9703bfca74d5fff0656b1879fc8189a)

![{\displaystyle \left[\left(x{\overline {\lor }}y\right){\overline {\lor }}x\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}y\right){\overline {\lor }}y\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b18aa26772bf982a90a7400a077c7f8482e15eee)

![{\displaystyle \left[\left(x{\overline {\lor }}x\right){\overline {\lor }}y\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}y\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a106b94d42c28f1fa6c0563b3368990dbd50328b)

![{\displaystyle \left[x{\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]{\overline {\lor }}\left[x{\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/60e3aada2cf1d960dcd7ae9e5b7b1d43566b61ad)

![{\displaystyle \left[\left(x{\overline {\lor }}x\right){\overline {\lor }}x\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}x\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8bc335e3197d5f3f0f9ecc80aa666768f9b0929d)